Dans le domaine des processeurs pour serveurs, Intel a attendu l'IDF pour lancer le Xeon E5-2600 v2 sur architecture Ivy Bridge, une semaine après avoir annoncé ses Atom C Series pour serveurs haute densité (Avoton). La performance de calcul pur du nouveau venu est bien supérieure à celle de l'actuel Xeon E5, pour une consommation énergétique améliorée, a pointé Jean-Laurent Philippe, directeur technique avant-ventes, Intel Europe de l'Ouest, lors d'un pré-briefing. « De génération à génération, la performance de chaque coeur est améliorée de 10 à 15% ». Au passage, il a rappelé qu'il restait encore beaucoup d'applications monothreadées (ne pouvant pas être réécrites ou n'étant pas parallélisables) ayant besoin d'un coeur tournant à une puissance très élevée, même si les OS et les développeurs d'applications exploitent de plus en plus le nombre de coeurs mis à disposition.

Le Xeon E5-2600 v2 est disponible en plusieurs versions dont la consommation descend jusqu'à 40 watts par socket, Intel garantissant aux fabricants de matériel qu'il leur faudra seulement alimenter et dissiper en 40 watts. « C'est très intéressant pour la haute densité ». En haute fréquence, le Xeon démarre dans une version 4 coeurs, pour les applications monothreadées ou très peu parallélisées. Il va jusqu'à 12 coeurs, avec une consommation de 130 watts (12 coeurs physiques hyperthreadés donc 24 coeurs logiques). « Il existe un processeur pour station de travail qui monte jusqu'à 150 watts pour faire tourner des codes comme Catia », a par ailleurs indiqué Jean-Laurent Philippe. Le Xeon E5v2 est compatible « hardware et software » avec la précédente génération de cartes mères Xeon E5 Sandy Bridge, mais sans bénéficier toutes les améliorations apportées. Typiquement, avec le nombre de coeurs, la bande passante mémoire a été augmentée (1866 contre 1600), et une carte de la génération précédente n'aura pas forcément été conçue pour le supporter, a rappelé Jean-Philippe Laurent.

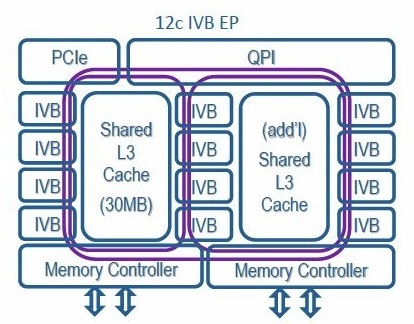

Trois bus entrecroisés sur l'Ivy Bridge-EP

Par rapport à l'architecture Sandy Bridge qui exploitait au maximum 8 coeurs, reliés par un double bus, tournant chacun dans un sens, pour relier les coeurs entre eux et au cache L3 (20 Mo), au contrôleur mémoire, au QPI (lien entre les processeurs physiques) et au PCI Express, le 12 coeurs Ivy Bridge-EP présente, lui, trois bus qui s'entrecroisent (ci-dessous en mauve), deux caches L3 dont une additionnelle (30 Mo sur la principale) et deux contrôleurs mémoire. Ce qui permet d'améliorer la gestion de tous les composants et la performance intrinsèque du processeur, a souligné le directeur technique qui décrit ce dispositif de bus comme extrêmement rapide : « d'une complexité inouie, mais d'une efficacité redoutable ».

Le Xeon E5-2600 v2 à 12 coeurs Ivy Bridge-EP

présente trois bus qui s'entrecroisent.

Une autre amélioration majeure du Xeon E5v2 réside dans sa capacité à générer des nombres de façon vraiment aléatoire pour le chiffrement et déchiffrement utilisés pour la gestion de la sécurité. Elle s'appuie sur des données liées à la température du processeur, ainsi qu'à d'autres sources, renforcées par les instructions AES pour générer un débit élevé de nombres aléatoires, de l'ordre de 6 Gb/s. La première génération de Xeon faisait déjà du décryptage rapide en recourant aux instructions AES.

Autre avancée importante sur le terrain de la sécurité, le SMEP (Supervisor Mode Execution Protection) qui permet d'empêcher, en cas d'attaque de type Stuxnet, qu'en ayant récupéré les droits du superviseur, il soit possible de rapatrier puis d'exécuter du code au niveau du bus 0. Les fréquences d'horloge des différentes versions de la puce Xeon E5v2 vont de 1.7 GHz pour le 10 coeurs E5-2650L v2 (70 watts) à 3,5 GHz pour le 4 coeurs E5-2637 v2. Ses prix s'échelonnent entre 202 et 2 614 dollars par quantité de mille.

IDF13 : Intel monte à 12 coeurs sur ses Xeon E5v2

0

Réaction

Dans sa version 4 coeurs, la consommation du Xeon E5v2 Ivy Bridge descendra jusqu'à 40 watts par socket. En 12 coeurs, elle monte à 130 watts.

Newsletter LMI

Recevez notre newsletter comme plus de 50000 abonnés

Commentaire