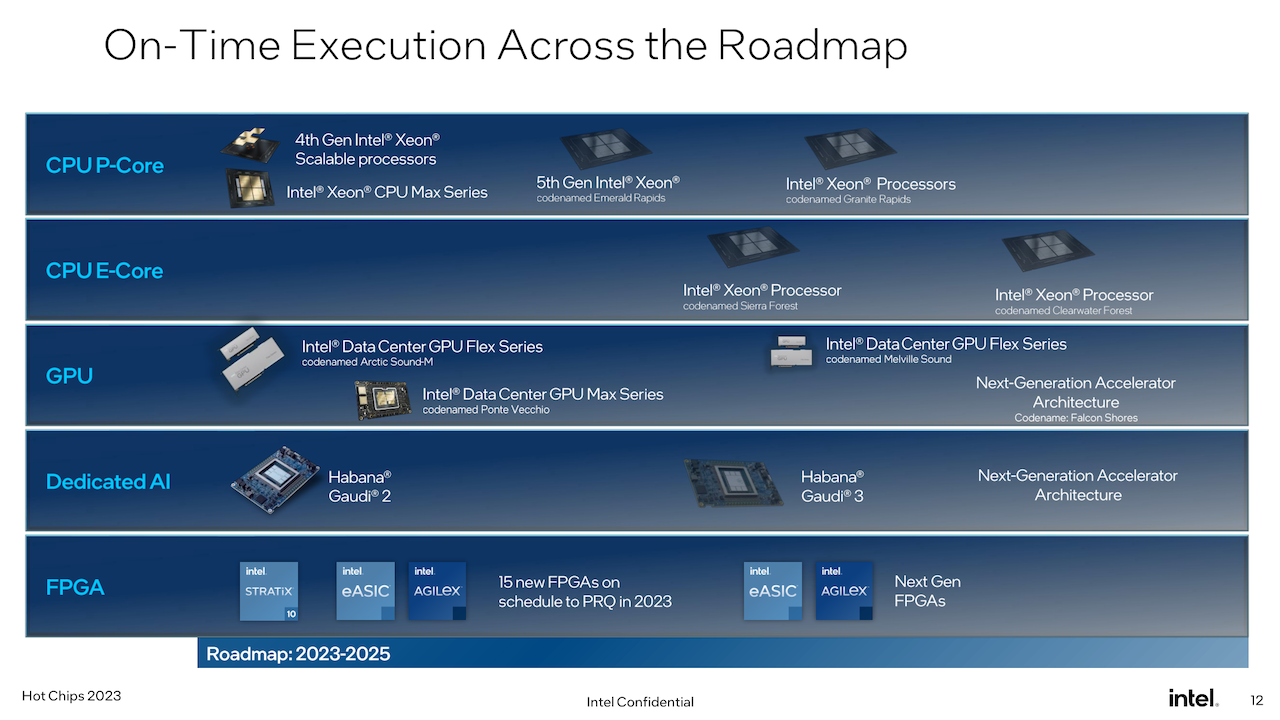

À l’occasion du salon Hot Chips 2023 (du 27 au 29 août à l’université de Stanford), Intel a mis en avant la cinquième génération de processeurs Xeon Scalable, noms de code Granite Rapids et Sierra Forest, dont la commercialisation est attendue en 2024. La dernière roadmap du fabricant de puces, présentée en mars dernier, avait déjà dévoilé quelques détails techniques sur l’architecture de ces puces pour serveurs. Granite Rapids et Sierra Forest s’annoncent déjà comme une mise à jour importante dans l’écosystème serveur d’Intel, grâce à l’introduction de cœurs E basse consommation (jusqu’à 144 cœurs par puce) et du support du CXL 2.0. Déjà intégrés aux puces grand public d’Intel depuis la 12e génération de Core (Alder Lake), les E-core (basse consommation) arrivent donc sur les Xeon Scalable. Contrairement aux composants grand public où les deux types de cœurs - performances et basse consommation - sont mélangés dans une seule puce, Intel opte pour une stratégie différente avec des Granite Rapids entièrement P-core et des Sierra Forest dotés d’E-core.

En tant que première puce Xeon Scalable E-core destinée aux datacenters (serveurs mono et bisocket pour charges de travail traditionnel et cloud), Sierra Forest est sans doute la plus importante des deux puces. À juste titre, il s’agit du premier Xeon gravé avec la technologie Intel3 basé sur EUV. Selon le fondeur, la livraison est programmée au premier semestre 2024. Également gravé en Intel3, Granite Rapids - de un à huit sockets pour les charges de travail exigeantes et l’IA - suivra juste après. La dernière plateforme ajoute le support d’instructions AMX supplémentaire (FP16) pour accélérer certains traitements. En complément, Intel a également présenté sa série Agilex 9 Direct-RF (FPGA)avec convertisseurs de données intégrés 64 Gsps (giga-échantillons par seconde) et une nouvelle conception de référence incluant des récepteurs à large bande et à bande étroite dans le même boîtier multipuce. Le récepteur large bande fournit une bande passante RF de 32 GHz au FPGA.

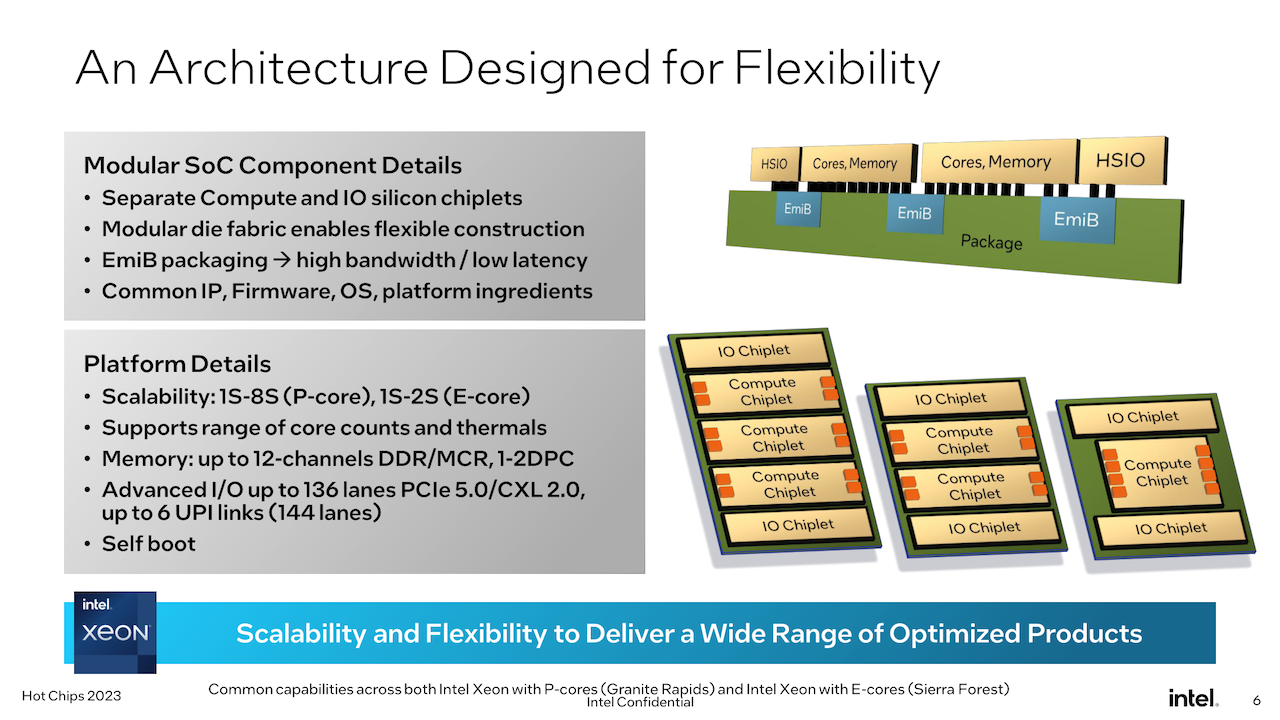

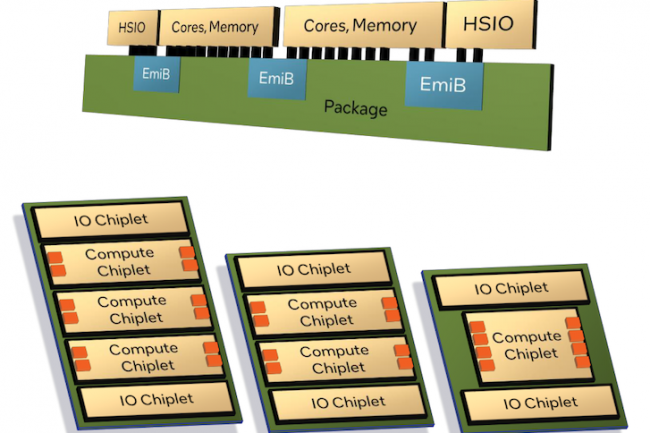

Intel étend l'usage de la technologie chiplet pour la conception de ses puces Xeon avec des briques modulaires. (Crédit Intel)

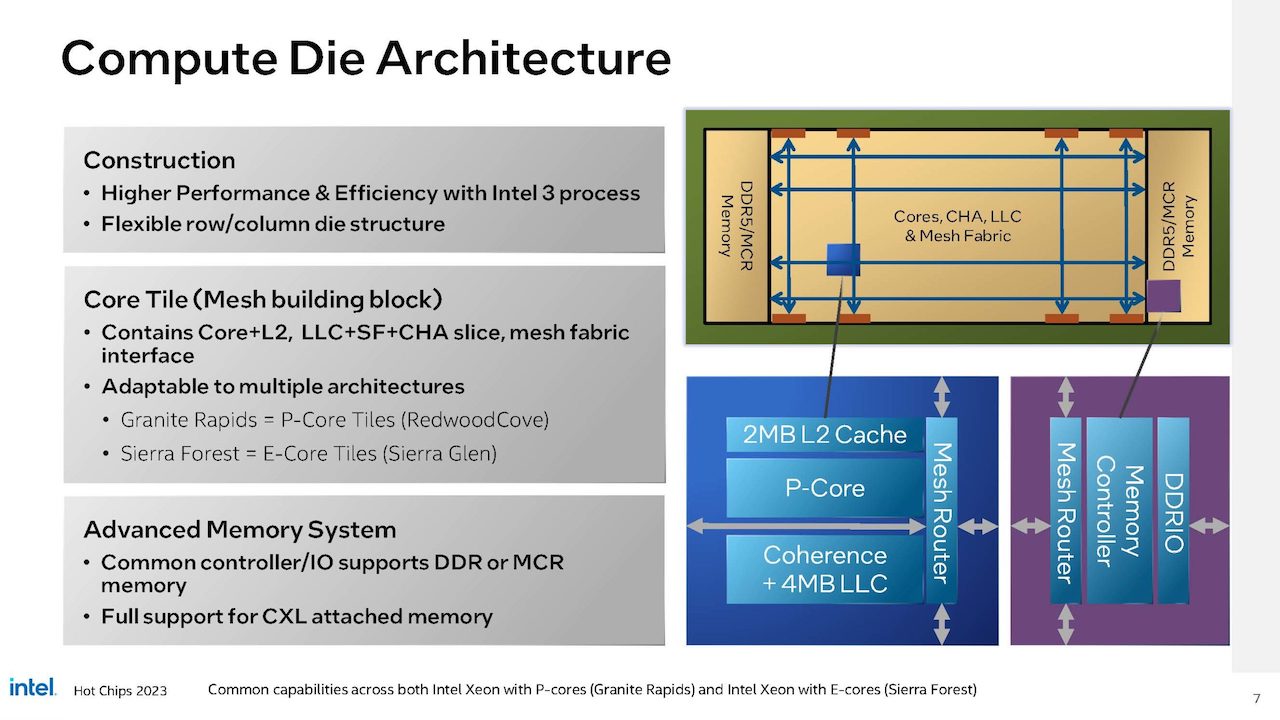

Comme annoncé par Intel en 2022, Sierra Forrest et Granite Rapids reposent sur une architecture chiplet, s’appuyant sur un mélange de briques compute et E/S assemblés à l’aide de la technologie de pont EMIB. Ce n’est pas la première fois que le fondeur produit des Xeon en mode chiplet, c’était déjà le cas avec le Sapphire Rapids, mais il s’agit d’une évolution de la conception chiplet utilisant des briques compute et E/S distinctes au lieu d’assembler des chiplets Xeon complets. Cela signifie que Sierra Forrest et Granite Rapids peuvent partager un chipslet d’E/S (fabriqué en Intel 7) et des chiplets compute E-core ou P-core (en Intel3). Pour les cœurs exploités avec les series E et P, Intel réutilise l’architecture de base inaugurée avec ses composants grand public. Ainsi, Granite Lake et Sierra Rapids peuvent être considérés comme un processeur Meteor Lake déconstruit, Granite obtenant les cœurs P de Redwood Cove, tandis que Sierra obtient les cœurs E de Crestmont, tous les deux inaugurés avec l’architecture Meteor Lake (Core 14e Gen).

Pour ses Xeon de 5e génération, Intel réutilise la base des coeurs exploités avec les Core Meteor Lake. (Crédit Intel)

Le fondeur confirme également que cette plate-forme Xeon Scalable dispose de capacités de démarrage automatique, ce qui en fait un véritable SoC. Le fondeur plaçant toutes les fonctionnalités d’E/S nécessaires au fonctionnement dans les chiplets d’E/S, un chipset externe (ou un FPGA) n’est pas nécessaire pour faire fonctionner ces processeurs. En termes de fonctionnalités, cela rapproche la gamme Intel Xeon de celle d’AMD, Epyc, qui démarre de la même manière depuis un certain temps maintenant. Au total, cette plate-forme Xeon Scalable prendra en charge jusqu’à 12 canaux de mémoire, évoluant en fonction du nombre et des capacités des cœurs présents. Comme précédemment indiquée par Intel, cette plate-forme sera la première à prendre en charge le DIMM Multiplexer Combined Ranks (MCR), qui regroupe essentiellement deux ensembles/rangs de puces mémoire afin de doubler la bande passante effective vers et depuis la DIMM. Grâce à la combinaison de vitesses de bus mémoire plus élevées et d’un plus grand nombre de canaux de mémoire, le fondeur affirme que la plate-forme peut offrir 2,8 fois plus de bande passante que les Xeon Sapphire Rapids Xeon actuels (4e génération).

Intel prévoit de lancer ses Xeon spécialisés au premier semestre 2023. (Crédit Intel)

Quant aux E/S, une configuration maximale Xeon pourra offrir jusqu’à 136 voies d’E/S, ainsi que jusqu’à 6 liaisons UPI (144 voies au total) pour une connectivité multi-socket. Pour les E/S, la plate-forme prend en charge PCIe 5.0 (le PCIe 6.0 est dans les cartons), ainsi que le protocole CXL 2.0 pour exploiter des ressources composables comme la RAM, les accélérateurs, la flash ou le réseau.

Commentaire