Il y a quelques mois, Samsung et Xilinx ont co-introduit un SSD avec un processeur FPGA Xilinx embarqué, afin d’apporter plus de capacité de traitement aux ressources de stockage. Le lecteur flash permet de traiter les données là où elles se trouvaient plutôt que de les déplacer vers et depuis la mémoire. Aujourd'hui, les deux fournisseurs poussent une mémoire à large bande passante (HBM) intégrée à un processeur IA, appelé HBM-PIM. Cette architecture de traitement en mémoire (PIM) permet d'intégrer les capacités d'intelligence artificielle dans la mémoire plutôt que de déplacer le contenu vers le processeur, afin d'accélérer le traitement à grande échelle dans les centres de données, les systèmes de calcul haute performance (HPC) et les applications mobiles utilisant l'IA.

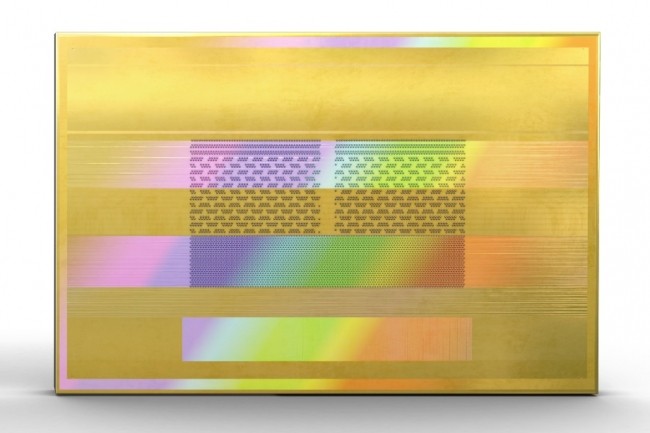

HBM est un type de mémoire différent de celui des DRAM. Elle est empilée verticalement plutôt qu'étalée en 2D, de sorte que les données se déplacent moins loin dans la mémoire. En conséquence, les puces HBM sont plus petites que les DRAM mais aussi plus chères, environ 30% de plus que les DRAM de capacité comparable. On retrouve les composants HBM principalement sur les CPU et les GPU, et ils sont généralement placés physiquement juste à côté de la puce afin de réduire les déplacements de données. Les applications nécessitant des ressources HPC et IA sont particulièrement indiquées pour exploiter ces capacités, car les budgets des entreprises sont plus importants que celui du grand public, gaming principalement.

Limiter les goulots d'étranglement mémoire

Samsung note que la plupart des systèmes informatiques actuels sont basés sur l'architecture von Neumann qui utilise des unités de processeur et de mémoire séparées pour effectuer les tâches de traitement des données. Cela signifie que les données sont déplacées dans les deux sens entre l'unité centrale et la mémoire, par le biais des bus chipset et processeur. Cette approche de traitement séquentiel exige que les données se déplacent constamment dans les deux sens, ce qui entraîne un goulot d'étranglement ralentissant le système, en particulier lors du traitement de volumes de données toujours plus importants. Depuis des années, les fournisseurs de CPU tentent de compenser en augmentant la taille des caches L1 à L3, au point qu'ils prennent plus de place que le cœur du CPU.

En revanche, l’architecture HBM-PIM apporte la puissance de traitement directement là où les données sont stockées en plaçant un moteur IA/DRAM optimisé à l'intérieur de chaque banque de mémoire - une sous-unité de stockage - permettant un traitement parallèle et minimisant le mouvement des données. Appliquée à la mémoire HBM2 Aquabolt de Samsung (16 Go avec une bande passante de 3,2 Gbit/s), cette architecture peut augmenter les performances du système – x2 selon Samsung - tout en réduisant la consommation d'énergie de plus de 70 %. Les barrettes HBM-PIM ne nécessitent pas non plus de modifications matérielles ou logicielles, ce qui permet une intégration plus rapide dans les systèmes existants.

« Notre HBM-PIM révolutionnaire est la première solution PIM programmable de l'industrie adaptée à diverses charges de travail basées sur l'IA, telles que le HPC, l’apprentissage et l'inférence. Nous prévoyons de tirer parti de cette avancée en poursuivant notre collaboration avec les fournisseurs de solutions d'IA pour développer des applications PIM encore plus avancées », a déclaré, dans un communiqué, Kwangil Park, vice-président senior de la planification des produits de mémoire chez Samsung Electronics.

Le HBM-PIM de Samsung est actuellement testé dans des accélérateurs d'IA par les principaux fournisseurs de plateformes IA, et toutes les validations devraient être terminées au cours du premier semestre de cette année.

Commentaire