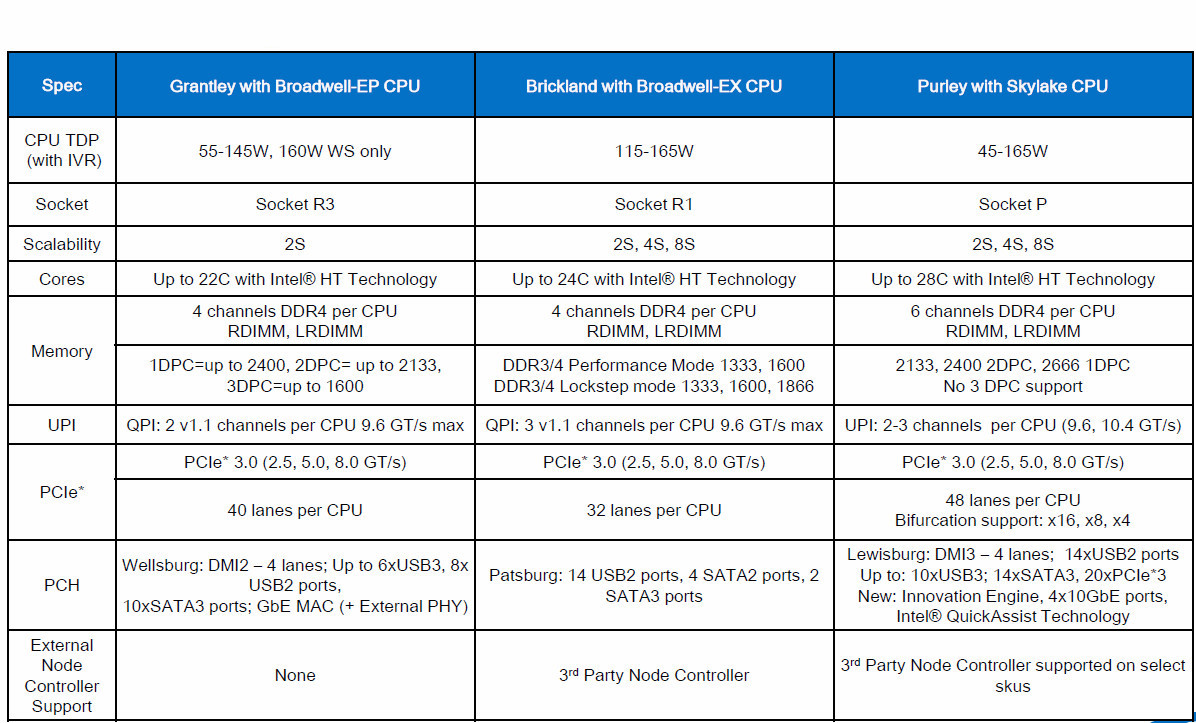

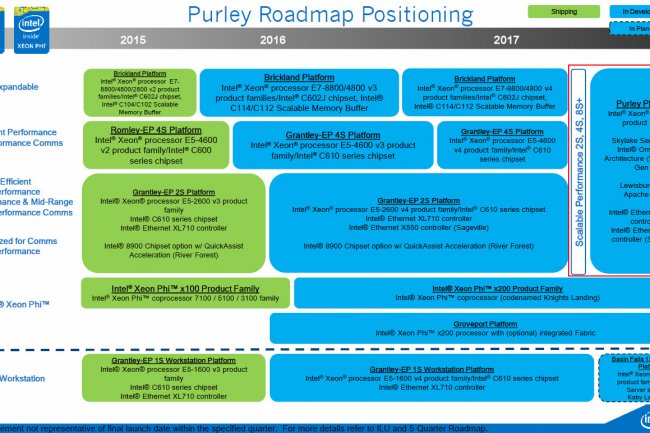

Pour succéder aux Xeon-E5 v4 Grantley (Broadwell-EP bi-sockets jusqu’à 22 cœurs) et Xeon-E7 v4 Brickland (Broadwell-EX 2, 4 et 8 sockets jusqu'à 24 coeurs) attendus fin 2016, Intel compte progressivement unifier ses Xeon 2, 4 et 8 sockets autour de la plate-forme Purley qui repose sur la microarchitecture Skylake gravée en 14 nm (comme Broadwell). C’est en tout cas ce que révèle la dernière roadmap processeurs Enterprise du fondeur. Toutes ces puces Purley exploiteraient un Socket-P, associé à la technologie d’interconnexion Omni-Path 100G (une évolution de la plate-forme Infiniband de QLogic rachetée en 2012) déjà employée dans les systèmes HPC en mode fabric. Grâce à l’emploi de câbles optiques, le débit pourrait atteindre 100 Gbits/s. Cette technologie est utilisable pour les communications internes et externes avec un contrôleur baptisé Storm Lake.

Fidéle à sa stratégie Tick-Tock (die shrink-new microarchitecture), Intel prévoit de lancer sa puce Xeon Purley en 2017.

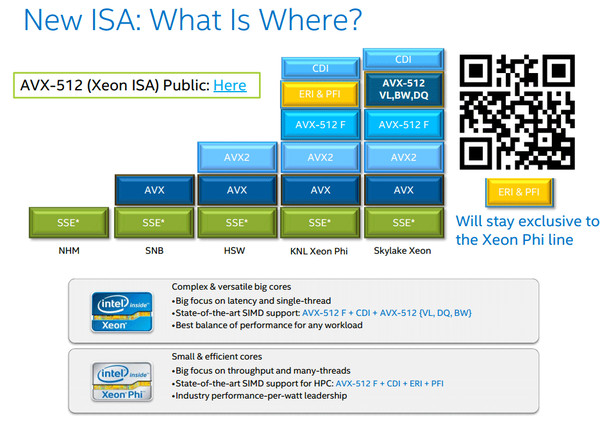

La plate-forme Purley inaugurera également le chipset Lewisburg avec un lien DMI3-bus par CPU capable de gérer jusqu’à 48 slots PCIe 3.0 et 4 interfaces 10 Gigabit Ethernet. Grâce à la finesse de gravure de Skylake, enrichie du jeu d’instructions AVX-512 comme sur les Xeon Phi, Intel pourrait monter jusqu’à 28 cœurs physiques par processeur, soit un total de 56 cœurs logiques si on active l’HyperThreading.

Après le Xeon Phi, le jeu d'instructions AVX-512 sera intégré au Xeon Purley/Skylane.

Les enveloppes thermiques (TDP ou Thermal Design Power) seront comprises entre 45W et 165W, en fonction du nombre de cœurs et des vitesses d'horloge. Le bus mémoire passe à 384 bits avec six canaux DDR4 2666 par CPU. Intel relance donc la course à la puissance pour répondre aux besoins des entreprises (base de données in-memory, consolidation de VM, et traitements analytiques) avec une plate-forme plus souple mais sans concession.

Commentaire