Dans le monde du datacenter, de plus en plus d’acteurs se servent de FPGA (fields programmable gate array) pour différentes tâches (réseau, sécurité, passage à l’échelle, IA). Grâce à ces puces programmables à la volée, la CPU peut être déchargé d’une grande variété de tâche. Il semble que la combinaison des deux intéresse AMD si on en croit un brevet déposé auprès de l’USPTO (Office américain des brevets et des marques).

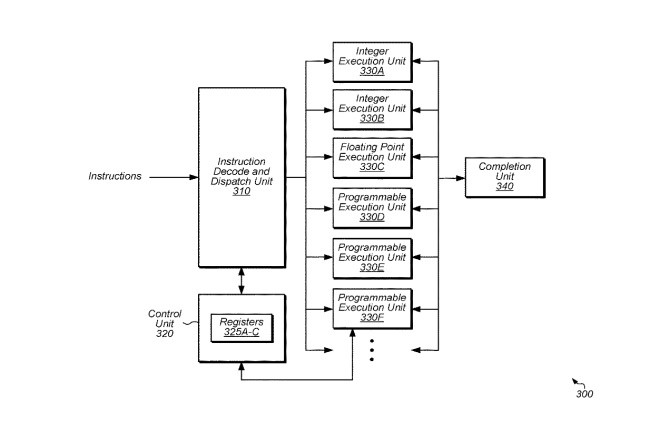

Repéré par HotHardware, ce brevet porte sur l'intégration d'unités de traitement programmables dans une CPU. Dans sa description, l’objectif de ce brevet est qu’un CPU peut inclure une ou plusieurs unités de traitement qui peuvent être programmées pour traiter différents types de jeux d'instructions personnalisées. Cela correspond à ce que fait un FPGA. Cela tombe bien, AMD a fait l’acquisition de Xilinx pour 30 milliards de dollars. La société est spécialisée dans les FPGA et les prometteurs SmartNIC.

Des applications avec du code dédié pour activer les FPGA

Dans le cadre du brevet, les développeurs pourraient intégrer facilement des instructions personnalisées dans les applications et le CPU serait capable de les transmettre au FPGA. Ces derniers pourraient ainsi traiter des données atypiques en particulier des valeurs FP16 (ou de demi-précision) qui servent aujourd’hui à accélérer la formation et l’inférence en IA.

Pour l’instant, on ne sait pas ce que va faire AMD avec ce brevet. En tout cas, l’intégration CPU/FPGA n’est pas prévue dans les récentes fuites sur les prochains processeurs Epyc. L’idée de cette combinaison n’est cependant pas nouvelle. Intel a déjà commercialisé en 2016 des puces Xeon Gold Xeon Gold 6138P épaulées par un FPGA fournie par Altera, qu'il avait racheté en juin 2015. L'exploitation de ces puces hybrides avec un CPU et un FPGA est toutefois plus complexe car il est nécessaire de combiner les instructions x86 et celles du FPGA. Un développement spécifique est à chaque fois nécessaire, mais les performances sont au rendez-vous notamment pour décharger le processeur central des traitements nécessaires à l'analyse de paquets IP par exemple.

Commentaire