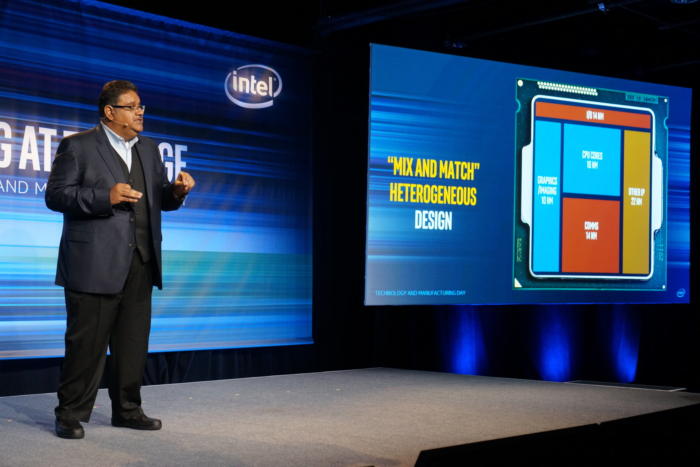

Les processeurs actuels tiennent tous sur une même plaque de silicium. « Mais ce mode de fabrication pourrait changer et il sera bientôt possible d’assembler plusieurs puces en créant entre elles une interconnexion haute vitesse », a déclaré Intel hier matin. Selon le fabricant, sa technologie Embedded Multi-die Interconnect Bridge, ou EMIB, permettra bientôt de connecter une puce de 22 nm à une puce de 10 nm et à une puce de 14 nm, pour créer un processeur. « Par exemple, nous pouvons mélanger des blocs de silicium haute performance avec des blocs de Silicium IP comportant des éléments basse consommation fabriqués à partir de cœurs différents, pour une optimisation maximale », a déclaré Murthy Renduchintala, président du Client, IoT, Businesses and Systems Architecture Group d’Intel (voir ci-dessous).

Le fondeur modifie radicalement le mode de production de la plupart de ses CPU et SoC, dont les composants sont habituellement fabriqués selon le même processus. Pour l’instant, Murthy Renduchintala n'a pas évoqué de prochaine puce SoC ou CPU utilisant la technologie EMIB. Il a simplement déclaré que cette technologie serait certainement appelée à jouer un rôle important dans les produits d’Intel à court et long terme. Ce dernier a également précisé que la technologie EMIB pouvait permettre d’atteindre des vitesses de « plusieurs centaines de gigaoctets/s », tout en réduisant par quatre la latence des techniques multi-puces traditionnelles. « L’EMIB représente vraiment une technologie de transformation pour Intel », a-t-il ajouté.

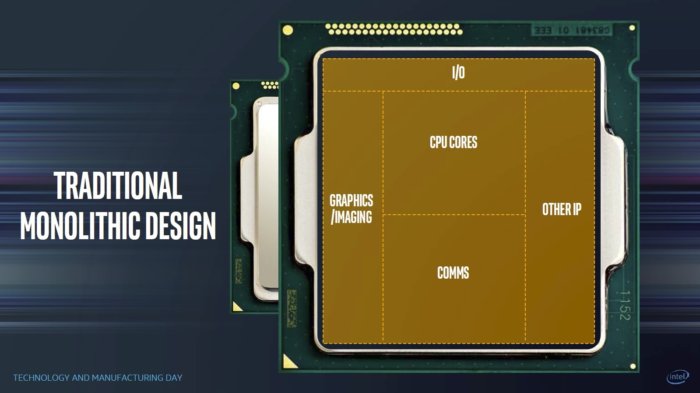

Les designs des processeurs actuels sont très monolithiques. Ils ne peuvent accueillir que des composants reposant sur le même processus de fabrication. (Crédit : Intel)

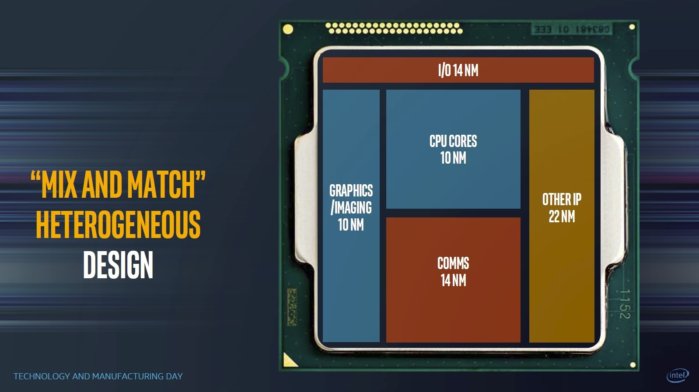

Avec la technologie EMIB, Intel pourrait produire un processeur et des cœurs graphiques sur la base d’un processus de pointe à 10 nm et l’assembler avec des composants basse consommation construits selon un processus à 14 nm. D'autres éléments pourraient bénéficier de la technologie. Par exemple, les circuits d’alimentation des designs à 22 nm pourraient s’ajuster avec d’autres circuits. À une époque, Intel voulait intégrer la régulation de tension dans ses puces Haswell de 4e génération et ses puces Broadwell de 5e génération. Mais le fondeur a abandonné l’idée pour ses puces Skylake de 6e génération et Kaby Lake de 7e génération. Selon certains, la mise à l'échelle du régulateur de tension à 14nm posait des problèmes. Mais l’EMIB pourrait réussir à maintenir le FIVR (Fully Integrated Voltage Regulators) à 22nm.

Les futurs processeurs d'Intel pourraient supporter plusieurs processus de fabrication. (Crédit : Intel)

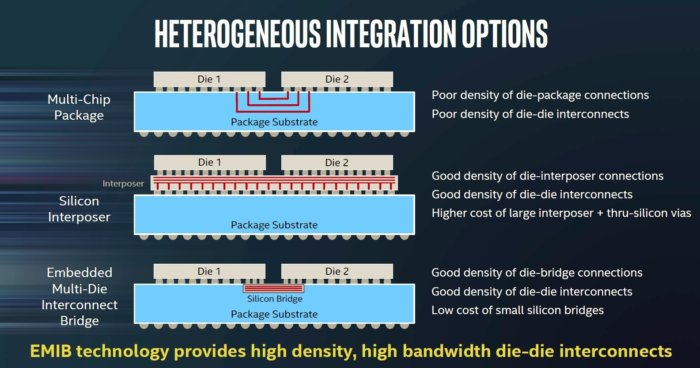

Ce n'est pas la première fois qu'Intel parle de fusionner deux puces en un seul processeur. A l’origine, le design du processeur Pentium Pro était multi-puce, tout comme la série de processeurs Core 2 Quad mais il s’agissait de produire rapidement des processeurs plus performants. Mais la technologie EMIB permet d’aller beaucoup plus loin et elle intervient au niveau du silicium lui-même. Dans un design multipuces traditionnel, les connexions sont gravées dans le substrat sur lequel sont montées les puces. Cette conception limite la quantité de fils et la vitesse des connexions. Un autre procédé consiste à utiliser un interposeur en silicium pour relier les substrats ce qui permet des densités et des performances plus élevées. Mais ce processus coûte cher. L’EMIB permet de combiner plus facilement les puces sans renoncer aux performances.

Selon Intel, l’EMIB (Embedded Multi-die Interconnect Bridge) est plus rentable que les méthodes basées sur un interposeur pour connecter des puces et ses performances sont bien meilleures que les designs multi-puces.

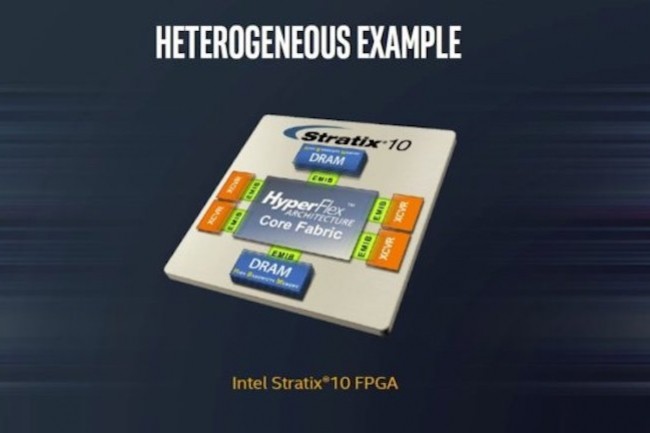

Même si Intel a effectivement parlé de l’EMIB lors de sa journée de présentation à la presse et aux analystes financiers de ses projets technologiques, la technologie n’est pas entièrement nouvelle puisqu’Intel l’a déjà mise en œuvre pour fabriquer les puces FGPA et SoC Altera Stratix 10.

Commentaire