Pour maximiser l’utilisation de l’apprentissage machine dans l’industrie 4.0, ARM étend les performances de ses architectures de SoC - system on chip - et de sa série de puces Cortex-M adaptées aux contraintes de taille, de puissance et de coût de l’IoT et des applications embarquées. Le concepteur britannique de puces vient d’annoncer le processeur Cortex-M55 secondé par le micro NPU Ethos-U55, unité de traitement neuronal. Cette association, conçue pour doper les capacités d’inférence du machine learning sur des équipements à basse consommation, va permettre de développer les cas d’usage. Le Cortex-M55 apporte jusqu’à 15 fois plus de performance sur l’apprentissage machine et jusqu’à 5 fois plus sur le traitement du signal comparé aux précédents processeurs de la série Cortex-M, indique dans un billet Thomas Lorenser, responsable produit senior chez ARM.

« C’est le premier à inclure la technologie ARM Helium, une extension de l’architecture Armv8.1, apportant 150 nouvelles instructions scalaires et vectorielles ». La puce est scalable pour les applications ML et elle est associée à l’Ethos-U55 pour les charges de travail plus complexes exigeant un rendement supérieur, explique-t-il. En 2021, ARM livrera des instructions spécialisées pour étendre encore les capacités du processeur sur l’optimisation de charges de travail spécifiques.

L'Ethos-U55 conçu pour la série Cortex-M

De son côté, l’Ethos-U55 est le premier microNPU conçu pour fonctionner avec la série Cortex-M, souligne ARM. En dehors des Cortex-M55, cela inclut les M33, M7 et M4. « Il est hautement configurable », pointe Thomas Lorenser, expliquant qu’il supporte des mises en oeuvre allant de 32 à 256 MACs (dans le traitement du signal) pour s’adapter aux différents marchés. En complément, ARM fournit une seule chaîne d’outils pour l’Ethos-U55 et le Cortex-M aux développeurs d’applications IA. Ceux qui ont déjà déployé du machine learning sur des équipements basés sur des Cortex-M pourront porter leurs développements vers la nouvelle technologie, indique ARM. « Tout est supporté par les bibliothèques open source existantes telles que CMSIS-NN et CMSIS-DSP et les frameworks de réseaux neuronaux comme TensorFlow Lite pour les micro-contrôleurs », précise Thomas Lorenser.

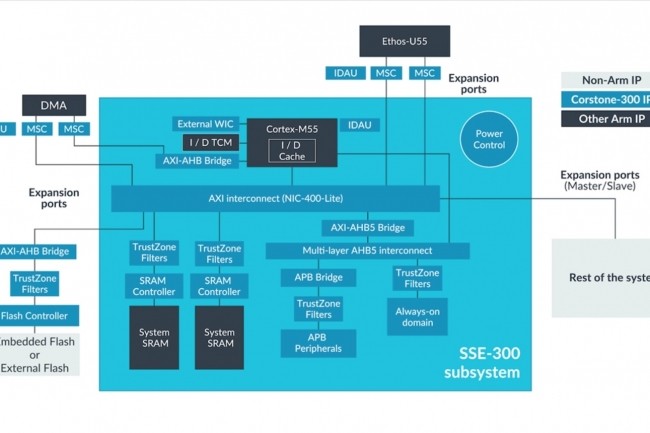

Design de référence Corstone-300

ARM fournit le design de référence Corstone-300 pour incorporer le Cortex-M55 dans un design de SoC, avec ou sans le microNPU Ethos-U55. Celui-ci renforce le niveau de sécurité avec la mise en oeuvre de la technologie TrustZone pour Armv8-M. Parmi les cas d’usage permis par ses nouvelles puces, le fournisseur britannique cite l’utilisation de la commande vocale avec davantage de traitements réalisés au niveau de l’équipement alors que ce genre d’applications nécessite actuellement de remonter une partie des traitements vers le cloud.

Commentaire