De futurs serveurs, attendus sur le marché dans les prochains mois, seront équipés de processeurs Intel Xeon Scalable Sapphire Rapids ou de puces AMD Epyc Genoa, avec une particularité : ils supporteront le protocole Compute Express Link (CXL), une norme d'interconnexion ouverte qui pourrait s’avérer très utiles, surtout dans les itérations futures. Pris en charge par pratiquement tous les fournisseurs de matériel, le CXL s'appuie sur le PCI Express pour assurer un accès cohérent à la mémoire entre un processeur et un périphérique, un accélérateur matériel (GPU, DPU ou FPGA) par exemple, ou entre un processeur et la mémoire.

Alors que le PCIe a été conçu pour les communications point à point, entre un SSD et la mémoire notamment, le CXL pourra prendre en charge les communications multidestinataires, ou « one-to-many », en transmettant des protocoles cohérents. Pour l’instant, dans son itération 1.1 actuelle, le CXL est juste capable de gérer une communication point à point, mais de nouvelles spécifications 2.0 et 3.0 ont déjà été annoncées. Comme le CXL est couplé au PCIe, ces versions de CXL dépendent des prochaines versions du PCIe. En moyenne, il se passe deux ans entre deux versions PCIe et il faut encore plus de temps entre la publication d'une spécification et la mise sur le marché des produits. Actuellement, les dispositifs CXL 1.1 et 2.0 sont au stade d’échantillons d'ingénierie pour tests.

Protocoles CXL

Il existe trois types de protocoles CXL :

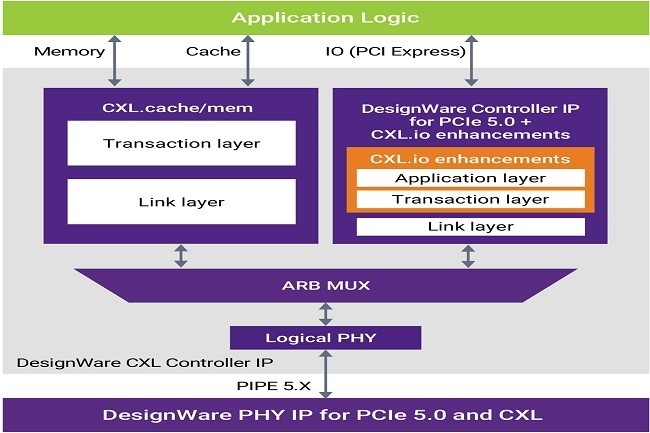

CXL.io : il s’agit d’une version améliorée du protocole PCIe 5.0 pour l'initialisation, la découverte du dispositif et la connexion au dispositif.

CXL.cache : Ce protocole définit les interactions entre un hôte et un dispositif, de façon à ce que les dispositifs CXL attachés puissent mettre efficacement en cache la mémoire de l'hôte avec une latence extrêmement faible en utilisant une approche de demande et de réponse.

CXL.mem : Ce protocole permet à un processeur hôte d'accéder à la mémoire d'un dispositif attaché, couvrant à la fois les architectures de mémoire volatile et persistante.

À partir de la version CXL 1.1, le protocole CXL.mem est le plus important des trois. Si un serveur a besoin de plus de RAM, il peut la trouver dans le module de mémoire CXL occupant un emplacement PCIe 5.0 vide. Les performances sont légèrement inférieures et il y a un peu plus de latence, mais en contrepartie, il fournit plus de mémoire dans un serveur sans avoir à l'acheter. Certes, les performances sont légèrement inférieures et il y aura un peu plus de latence, mais c'est un maigre compromis pour bénéficier de plus de mémoire dans un serveur sans avoir à l'acheter. Évidemment, il faut acheter le module CXL.

Le protocole CXL 2.0 prend en charge la mise en commun de la mémoire, c’est-à-dire qu’il peut utiliser la mémoire de plusieurs systèmes plutôt que d'un seul. Selon Microsoft, environ 50 % de toutes les VM ne consomment jamais la moitié de leur mémoire louée. Le CXL 2.0 pourrait ainsi trouver et se servir de cette mémoire inutilisée. Selon Microsoft, la désagrégation via CXL peut permettre de réduire de 9 à 10 % le besoin global en DRAM. À terme, le CXL devrait s’imposer comme interface avec le cache pour connecter de manière cohérente un nombre illimité de CPU, de modules mémoires, d'accélérateurs de processus (notamment les FPGA et les GPU) et d'autres périphériques. La spécification CXL 3.0, annoncée lors du Flash Memory Summit (FMS) organisé du 2 au 4 août à Santa Clara, Californie, va encore plus loin dans la désagrégation puisqu’il permet à d'autres composants de l'architecture - processeurs, stockage, réseau et autres accélérateurs - d'être mis en commun et adressées dynamiquement par plusieurs hôtes et accélérateurs, tout comme la mémoire dans la spécification 2.0. La spécification 3.0 prévoit également des communications directes entre pairs par le biais d'un commutateur ou même d'un fabric de commutation, de sorte que deux GPU pourraient théoriquement communiquer entre eux sans utiliser le réseau ou impliquer le CPU et la mémoire de l'hôte.

Kurt Lender, co-président du groupe de travail sur le marketing de CXL et responsable principal de l'écosystème chez Intel, a déclaré : « Le CXL sera présent partout. Les informaticiens ne seront pas les seuls à l'adopter. Tout le monde va l'adopter. Au cours des prochaines années, le CXL va à devenir un standard de tous les nouveaux serveurs ». Dans les datacenters d’entreprise, le CXL peut apporter beaucoup de choses. Selon M. Lender, parce que le CXL fonctionne au niveau du système, la plupart des applications n'ont pas besoin d’être modifiées, et pourront bénéficier des avantages de la fonctionnalité. « Par exemple, les bases de données en mémoire peuvent profiter de la mise en commun de la mémoire », a-t-il ajouté. Cette mise en commun des composants pourrait fournir une partie des ressources nécessaires à l'IA. En effet, grâce à cette mise en commun des CPU, GPU, FPGA et ports réseau, des datacenters entiers pourraient se comporter comme un système unique. Mais, inutile de s’emballer. Il faut encore attendre l’arrivée de produits supportant le CXL 2.0. Les démonstrations faites lors du récent salon FMS laissent penser que l’on en trouvera bientôt sur le marché. Signalons pour conclure que des start-ups comme Fungible ou Liqid n'ont pas attendu l'arrivée de cet protocole pour commercer à exploiter des ressources désagrégées dans un datacenter.

Commentaire